《炬丰科技-半导体工艺》 碳化硅大功率高频电

书籍:《炬丰科技-半导体工艺》

文章: 碳化硅大功率高频电子器件上的薄氮化镓

编号:JFKJ-21-1162

作者:华林科纳

?

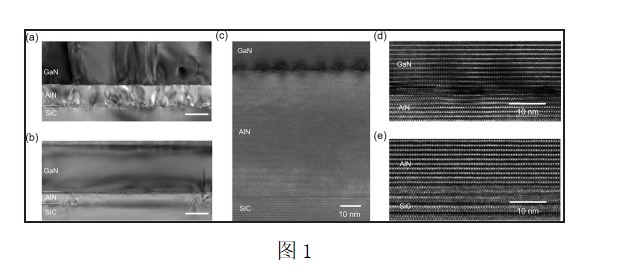

?在碳化硅(SiC)上开发了更薄的III族氮化物结构,以期实现高功率和高性能高频薄高电子迁移率晶体管和其他器件。新结构使用高质量的60纳米无晶界氮化铝成核层来避免大面积的扩展缺陷,而不是1-2米厚的氮化镓缓冲层(图1)。成核层允许在0.2 m内生长高质量的氮化镓。

图1?使用(a)常规和(b)低TBR氮化铝成核在氮化镓/氮化铝/碳化硅界面沿[112–0]方向的横截面透射电子显微图像。氮化镓/低TBR氮化铝纳米线/碳化硅的高倍放大图像。氮化镓/低TBR氮化铝纳米线界面的高分辨率图像。(e)低TBR氮化铝纳米线/碳化硅界面的高分辨率图像。比例尺在(a)和(b)中为100纳米。

通常较厚的缓冲层用于过渡和减少由氮化镓和碳化硅之间3.5%的晶格失配引起的缺陷——对于蓝宝石和硅等其他衬底,失配要高得多。这些厚层给高功率和高频器件带来了问题。这些层通常掺杂碳或铁以增加电阻,目的是限制电流流向沟道区,避免寄生传导的泄漏效应。掺杂会产生电荷俘获状态,从而对电流等性能产生负面影响在射频操作中崩溃。

更薄的器件还应该具有更低的热阻,从而改善热管理。在GaN/AlN/SiC界面产生的空隙和位错等结构缺陷引入了热边界电阻(TBR),导致HEMTs中的沟道温度额外上升30–40%。

所需昂贵材料的减少是这项工作的另一个吸引力。包括前体和气体在内的原材料将减少90%,同时由于所需的生长时间减少,加工成本也将降低。

新的氮化铝成核过程避免了通常的晶粒状形态,这种形态往往会导致柱状生长,缺陷会被带入上方的氮化镓中。通常的颗粒性是由于生长表面上铝原子的低迁移率。

在硅面4H碳化硅上生长第三族氮化物材料。热壁金属有机化学气相沉积(MOCVD)被用于产生具有60纳米AlN成核、200纳米GaN沟道,高达1.5纳米的氮化铝夹层、10–14纳米的铝镓氮阻挡层(~30%铝)和2纳米的氮化镓帽。60纳米氮化铝是利用热壁生长的低热边界电阻(低TBR)技术生产的。尽管该结构很薄,但估算了低108/cm2范围内的穿透位错密度,

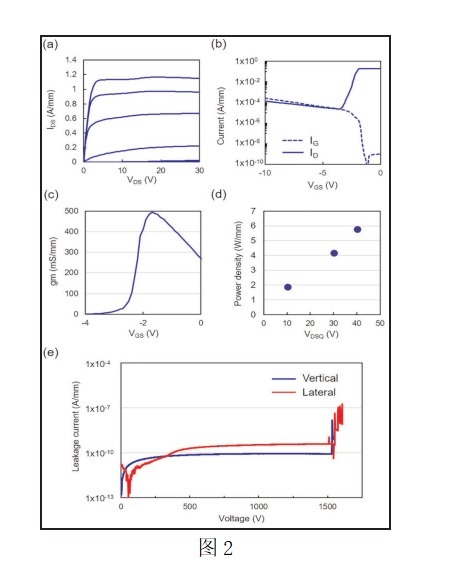

比相同厚度的典型GaN层小两个数量级。在具有2纳米氮化镓帽和14纳米铝0.29镓0.71氮势垒的结构上进行的非接触霍尔测量给出了9.8×1012/cm2的二维电子气体密度和2050cm2/V-s的迁移率。薄层电阻为315ω/平方。在具有2纳米氮化镓帽、10纳米铝0.3镓0.7氮阻挡层和1纳米氮化铝中间层的材料上生产测试晶体管。源极/漏极采用基于Tanta- lum的触点,接触电阻为0.3ω-mm。该器件实现了1.1A/mm的高导通电流密度和1.3ω-mm的低归一化导通电阻(图2)。

图2(a) DC漏极电流-电压(IDS–VDS)特性,(10V漏极偏置下的传输特性和栅极与漏极电流(VDS)作为栅极电压的函数(VGS),(c)跨导(gm)作为栅极电位的函数,以及(d)射频输出功率密度作为T-HEMT的VDSQ的函数。没有顶部有源层的异质结构的垂直和横向击穿特性。

饱和电流保持在30V漏极偏置。当漏极偏置为10V时,夹断现象明显,跨导达到500mS/mm。亚阈值摆幅取决于栅极长度:0.1 m为250mV/10,0.2 m为130mV/和0.2 m栅极的击穿电压分别为70V和140V。

击穿电压和栅极长度之间的线性关系表明,由于栅极长度和栅极到漏极间距的尺寸有限,击穿是横向发生的。”栅极-漏极间距为2米,远低于通常用于氮化镓高迁移率晶体管的10-20米表现。此外,传统的氮化镓功率HEMTs具有微米级的栅极长度。在30千兆赫下的负载牵引测量给出了40V漏源静态偏置(VDSQ)下5.8W/mm的峰值射频功率密度。

在没有上部氮化铝/氮化铝镓层的外延叠层上的击穿测量给出了在横向和垂直方向上高达1.5kV的击穿电压。在这两种情况下,故障都是由于接触的不良描绘。因此,电池堆的实际击穿电压预计会更高。换句话说,击穿受到表面的限制,这证实没有界面载流子。

?

文章来源:《电子元件与材料》 网址: http://www.dzyjyclzz.cn/zonghexinwen/2021/1215/865.html

上一篇:格力电器收购制冷元器件行业龙头向上游新能源

下一篇:没有了